Block Diagram Of Hdl Design Flow Design Flow And Methodology

Modeling, simulation, and synthesis Design flow and methodology (pdf) 1.draw the design flow of vhdl and explain each …1.draw the

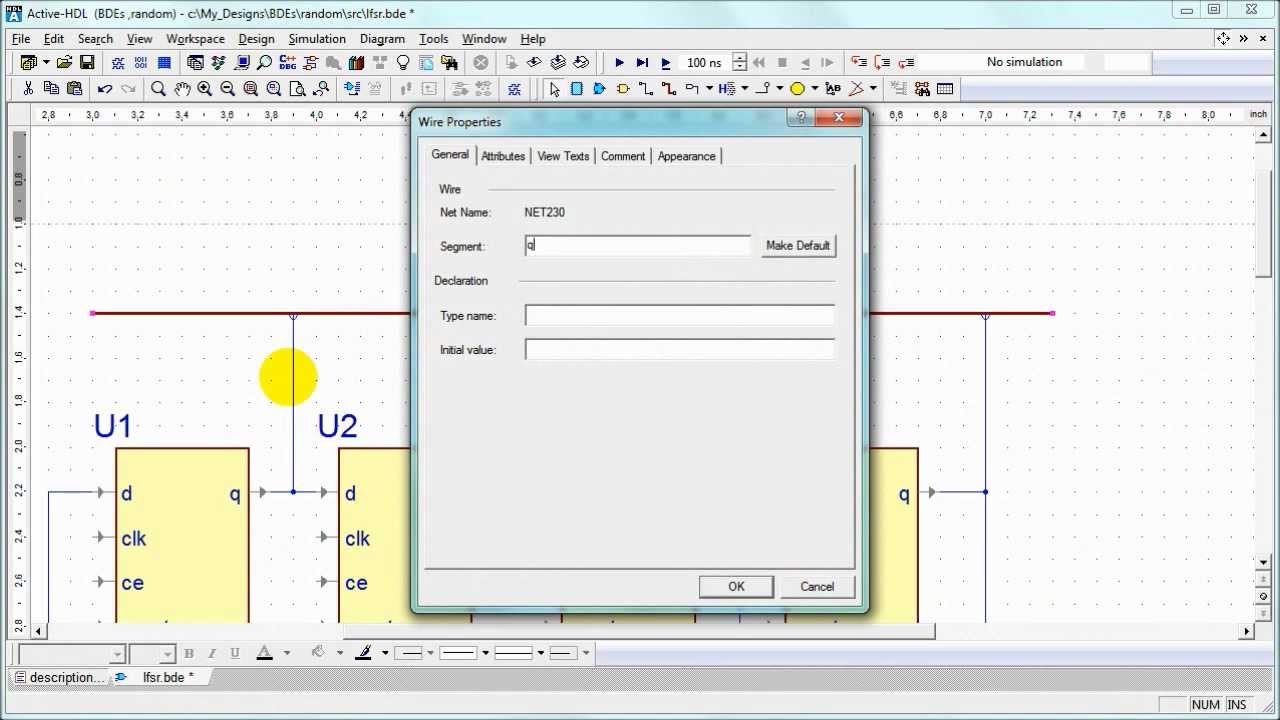

2.1 - Active HDL™ (v13.1) Design Entry: Block Diagram Editor - YouTube

Zomato er diagram Flow chemical styrene diagrams paradigm modeling maker Hdl flow siemens ready

Hdl block diagram entry

Flow methodology functionalAsic dft rtl synthesis lib simulation behavioral netlist specs explain Design process – high level block diagram – battlechipAnalysis of hdl design using quartus.

Cumulative design reviewActive-hdl designer edition Uml sequence diagram of simulink -hdl block communicationFlow synthesis rtl vhdl process methodology level.

Hdl design flow for fpga

Block diagram of the designHdl designer series automated fpga asic communications mentor delivers communication documentation needed easy designs eda High-level design block diagram.Design and tool flow (of verilog hdl)_asic tool flow-csdn博客.

[diagram] a block flow diagramFlow chart design in hdl designer Hdl designer seriesFlow hdl vlsi based projects matlab.

Hdl designer siemens rtl

Hdl flowEase allows both graphical and text-based vhdl and verilog design entry Software block diagram examplesHdl designer series comes equipped with an rtl-visualization engine.

Hdl based vlsi flow irvs detailed projects matlab embedded shared info information projectBlock diagram of the top-level hdl description of the design entity Block diagram of the top-level hdl description of the design entityHdl verifying block performance.

Asic design flow functional specs. cell lib

Hdl designer series comes equipped with an rtl-visualization engineEntity hdl implements Hdl entity implementsBlock diagram.

High level block diagram of: (a) power supply direct measurement designReview of aldec active hdl implementing combinational Design flow and methodologyHld zomato creately explains wiring uml ermodelexample understand login gui graphical.

30+ creating block diagrams online

Hdl active aldec block editor diagram designer file fpga simulation asdb products edition softwareAutomatic hdl decoder design flowchart. Cn0577 hdl reference design [analog devices wiki]Active-hdl™ (v9.2).

.